Low Voltage CMOS logic

DATA HANDBOOK

**Philips Semiconductors**

**PHILIPS**

9

B 0 0 K

Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustration purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

## LIFE SUPPORT APPLICATIONS

Philips Semiconductors' products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors product can reasonably be expected to result in a personal injury. Philips Semiconductors customers using or selling Philips Semiconductors Products for use in such applications do at their own risk and agree to fully indemnity Philips Semiconductors for any damages resulting from such improper use or sale.

# LOW VOLTAGE CMOS LOGIC FAMILIES; HLL AND LV-HCMOS

| Preface                                                                          |  |

|----------------------------------------------------------------------------------|--|

| Introduction                                                                     |  |

| Numerical index                                                                  |  |

| Ordering information                                                             |  |

| Family Specifications  HLL family characteristics                                |  |

| Definition of symbols                                                            |  |

| Quality  Quality at Philips Semiconductors  Rating systems  Handling MOS devices |  |

| Definition of Data Sheet Status                                                  |  |

| Survey of pinouts  HLL family                                                    |  |

| Device data                                                                      |  |

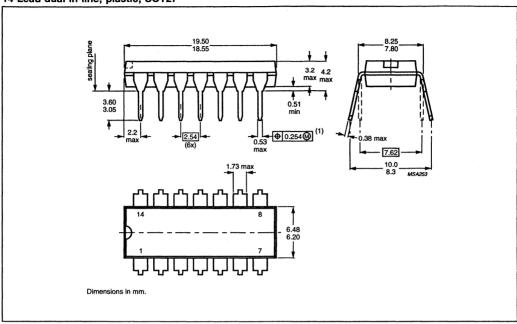

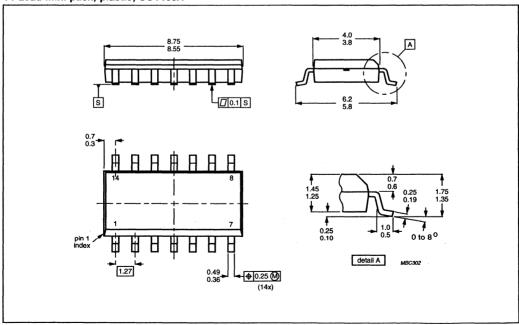

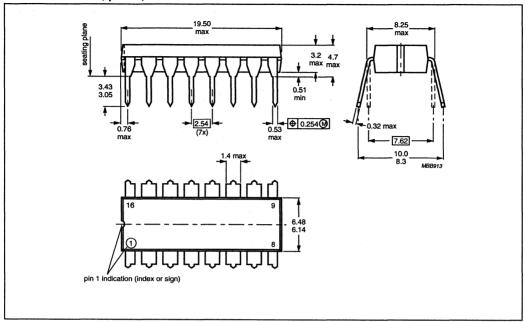

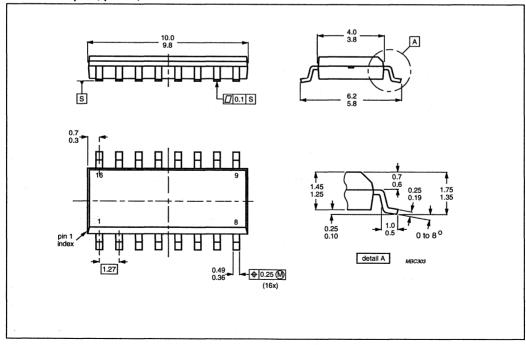

| Package information Outlines Soldering                                           |  |

## **Preface**

Philips Semiconductors would like to thank you for your interest in our new low voltage CMOS logic families. The families HLL (High speed Low power Low voltage) and LV-HCMOS (Low Voltage High Speed CMOS) are optimized for applications working at 3.3 V, the standard supply voltage for may new digital systems. In addition they are guaranteed for operation at voltages as low as 1.2 V making them an ideal choice for many portable applications.

A detailed introduction to both new families can be found on page 3.

In addition to HLL and LV-HCMOS Philips Semiconductors offers the industry's most advanced line of logic products which, apart from a number of well established ranges of bipolar and CMOS families, include ABT (Advanced BiCMOS), MULTIBYTETM and Futurebus+.

Philips Semiconductors shows a continuous innovation, bringing new product lines which are needed for novel designs. Information regarding these and other families can be obtained from your nearest Philips Semiconductors' representative or authorized distributor.

Philips Semiconductors Logic ICs

## Fast, low-power HLL & LV-HCMOS logic families

The heavy load imposed on electronic data processing (EDP) equipment by the ever-increasing complexity of modern software has led to the recent entry into the market of desktop computers and other EDP equipment using fast '386, '486, '586, 680x0 and RISC processors. This, in turn, has caused a demand for very fast low-power portable EDP equipment such as laptop computers, mobile radios, hand-held video games, telecom equipment and instrumentation.

To satisfy equipment manufacturers' component needs for this faster and/or lower power type of equipment, many new 3.3 V ICs such as the microprocessors mentioned above, static and dynamic memory, ASICs, disk controllers and flatpanel LCD controllers are now appearing on the market. This has added considerable momentum to the demand for fast, low-voltage 'glue logic' ICs to complete the chip-sets for fast, low-voltage EDP applications.

Philips has responded to this demand by developing the two

new low-voltage CMOS logic families which are specified in this data handbook, to complement our existing range of logic ICs.

The new families are:

- HLL (High speed Low-power Low-voltage) logic

- LV-HCMOS (Low-Voltage High-speed CMOS) logic. Both families have the wide supply voltage range (1.2 V to 3.6 V) and very low power consumption to make them an ideal choice for battery or mains-powered EDP applications where high speed and low power consumption are prime considerations.

### REDUCING THE SUPPLY VOLTAGE FOR CMOS LOGIC WITHOUT LOSING SPEED

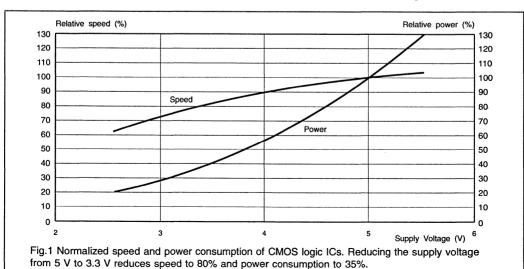

As shown in Fig.1, the power consumption of CMOS logic ICs diminishes approximately with the square of the supply voltage reduction. An obvious method of minimizing the power consumption of these circuits is therefore to reduce the conventional nominal supply voltage of 5 V to 3.3 V. Figure 1 shows that this reduction of supply voltage reduces the

power consumption by about 65% and is accompanied by a speed reduction of only 20%. The immediate advantages gained simply by moving from 5 V to 3.3 V operation are therefore that the speed/power ratio for CMOS logic ICs is more than doubled, and it becomes possible to power them from a 1 or 2-cell battery in portable equipment.

The reduction of maximum speed resulting from the supply voltage reduction can be restored, and even increased, by using finer geometry and sub-micron CMOS technology which is tailored for low-power and low-voltage applications.

#### THE NEW HLL AND LV-HCMOS LOGIC FAMILIES FROM PHILIPS

We have used both supply voltage reduction and speed enhancement techniques for our new HLL and LV-HCMOS families of logic ICs.

Features common to both families

Wide supply voltage range of 1.2 V to 3.6 V allows operation from a regulated mains-derived

supply or an unregulated battery supply

- In accordance with the JEDEC LV standard (8.1) of 3.3 V ±0.3 V for ICs powered from a regulated supply

- Fabricated in CMOS for intrinsic low power consumption - only a few nanoamps of supply current flow in the static state

- Push-pull outputs that swing from rail to rail - the reduced voltage swing with a low-voltage supply reduces power consumption dramatically and also improves EMC and EMI; particularly important for portable RF equipment

- Minimal over-shoot and under-shoot noise

- · Latch-up free operation

- · Excellent ESD protection

- · Low ground-bounce

- Improved system reliability due to lower power dissipation and minimized gate oxide thermal breakdown voltage

- · Symmetrical waveforms

- Lowered power consumption allows:

- smaller and lighter batteries

- ✓ longer periods between battery charges

- increased PCB packing density

- ✓ reduced power supply costs

#### Features of the HLL family

HLL is an entirely newly designed logic family from Philips. It comprises extremely fast lowpower logic ICs designed from scratch and fabricated in a submicron CMOS process with twolevel metal and epitaxial substrates. HLL ICs with a 3.3 V ±0.3 V supply operate at twice the speed of FAST bipolar logic and, because they are CMOS ICs, they consume only a small fraction of the power. The family functions are mainly tailored for very high speed operation in the data-intensive bus interface area of mains-powered EDP equipment with a regulated 3.3 V supply.

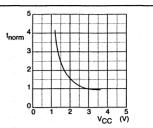

However, since they also function, at reduced speed (see Fig.2), with supply voltages down to as little as 1.2 V, HLL ICs can also be used in battery powered equipment.

Specific features of the HLL family are:

- Supply voltage 3.3 V ±0.3 V for maximum speed applications in equipment with regulated power supplies; 1.2 V to 3.6 V for battery powered equipment

- High dynamic output drive allows transition times to be much shorter than the propagation delay

- Sub-micron technology allows typical propagation delay of 2.5 ns with a 3.3 V supply twice the speed of FAST with a 5 V supply

- Low-inductance, multiple centre power and ground pins for minimum noise and groundbounce

- With a 3.3 V ±0.3 V supply, inputs and outputs interface directly with TTL levels

- Output edge-rate control circuitry for significantly less noise generation

- Reverse-biased diode (to ground only) at each input to limit line reflections

- The input voltage can exceed the supply voltage (up to 5.5 V), so HLL can be used for 5 V to 3 V and 3 V to 5 V level shifting in mixed 3 V/5 V systems

- SO and SSOP packages for surface mounting

# Features of the LV-HCMOS family

This low-voltage CMOS logic family is based on Philips' well-known HCMOS (HC) range and uses the same well-proven fabrication process with only slight modifications. It operates from a typical supply voltage of 3.3 V but can be used within the supply voltage range 1.2 V to 3.6 V. With a 3.3 V supply, the speed and performance is the same as HCMOS with a 5 V supply, so there are absolutely no disadvantages when replacing 5 V

Fig.2 Normalized derating curve for typical propagation delay (t<sub>p</sub>).

#### CMOS logic with LV-HCMOS.

To obtain the speed and output drive of HCMOS at the lower supply voltage, the channel length for LV-HCMOS is reduced to 2  $\mu$ m, the gate oxide is thinner and the threshold voltages are lowered. Functions are a sub-set of the HCMOS family functions. Specific features of the LV-HCMOS family are:

- Process tuned for low-power applications with supply voltages between 1.2 V and 3.6 V

- Output drive at V<sub>CC</sub> = 2 V is 4 mA (6 mA for driver outputs)

- Speed at 3 V is virtually the same as that of HCMOS at 5 V

- Faster than HCMOS at lower supply voltages

- Requires minimal qualification by the user because it is produced in our established HCMOS wafer fab. with a process that varies little from the standard HCMOS process

- Pin- and function-compatible with HCMOS ICs

- Identical high quality standards as for all Philips' HCMOS ICs.

- SO and SSOP packages for surface mounting

# SUPPLY VOLTAGE CONSIDERATIONS

There are three main reasons for reducing the supply voltage of logic ICs:

- To allow them to be used in portable battery powered equipment

- To reduce power consumption

(dissipation) so that the size and weight of equipment can be reduced and portable equipment can function for longer periods without re-charging the battery

To meet demands for faster, high-performance operation, ICs must be fabricated with finer process geometry which requires a lower supply voltage.

Other benefits of a low supply voltage include lower noise levels, reduced EMI, and improved reliability due to reduced stresses on the ICs.

There is not vet a well-defined industry standard for low-voltage operation, but a level of 3.3 V ±0.3 V seems to be common for equipment with a regulated supply and is also proposed by JEDEC. For battery operation, the requirements are more stringent because the supply voltage variation is greater. For example, at the end of their operating life, a pair of Alkaline or Carbon Zinc batteries can only supply about 1.8 V, and a single NiCd cell provides only 1.2 V just before it needs re-charging. The wide supply voltage range and output drive levels of HLL and LV-HCMOS ICs allows them to be powered from any of these sources.

#### POSITIONING OF HLL AND LV-HCMOS WITH RESPECT TO OTHER LOGIC FAMILIES

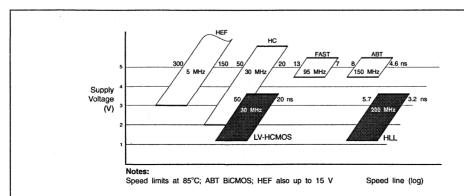

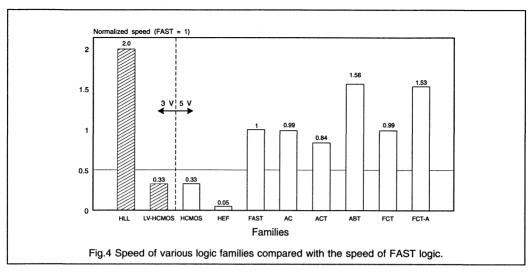

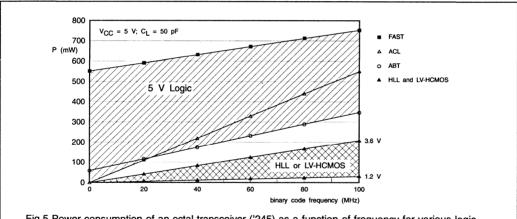

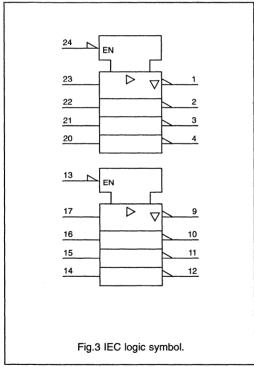

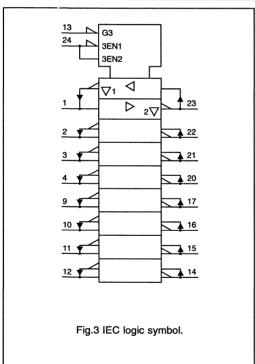

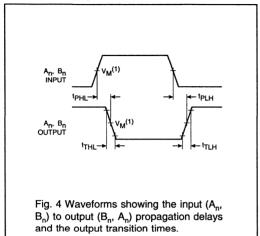

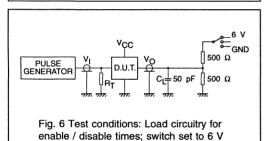

Figures 3, 4 and 5 are included here for clarification purposes only.

Figure 3 shows speed as a function of supply voltage for Philips CMOS logic IC families. Figure 4 shows the speed of most advanced logic families compared to the speed of FAST logic ICs.

Figure 5 shows power consumption as a function of speed for an octal transceiver from various logic families. Each output of the IC is loaded with 50 pF and the eight transceivers in the device are each driven by one bit of an 8-bit binary code that counts from 00000000 to 11111111. The transceiver driven by the least-significant bit is therefore running at the highest frequency, and the transceiver driven with the most-significant bit is running at a frequency 2<sup>7</sup> times lower.

#### The HLL family

Figure 3 shows that the extreme speed of HLL makes it a clear extension to Philips' range, complementing our other logic families. Users needing low power consumption or with data-intensive applications can derive full benefit from HLL.

Figure 4 indicates that the speed

of HLL is exceptional when compared to other logic families. As is common practice, the speeds in Fig.4 are referenced to FAST logic. By attempting to emulate, or even improve on FAST logic speed, many new logic families appearing on the market put signal integrity at stake. This is why Philips believes that the proven low-impedance multiple centre power supply pinning used for HLL will become an industry standard for very fast logic. The background for this is the effect of groundbounce. Groundbounce not only affects signal integrity, it also affects the propagation delays when all outputs are switching. It is simply impossible to make CMOS devices with corner pin which combine the extreme speeds as provided by HLL during simultaneous switching. In addition centre-pin devices provide low skew and improved EMC.

As expected for CMOS products with their intrinsic low static power consumption, Fig.5 shows that, in the idle state and at low frequencies, HLL ICs consume negligible power. In the idle state, power consumption is only 0.25 mW, and at 1 MHz it is a mere 0.9 mW. This makes HLL very attractive for applications where short propagation delays are essential and low dissipation is required. With a 3 V supply at 100 MHz, power consumption for

Fig.3 Guaranteed speed as a function of supply voltage for Philips logic ICs. The speed range per logic family is due to the different functions within the families.

Fig.5 Power consumption of an octal transceiver ('245) as a function of frequency for various logic families.

HLL is between 60% and 80% less than for other advanced 5 V logic families.

## The LV-HCMOS family

From Fig.3 and Fig.4, it can be seen that, with a 3.3 V supply, LV-HCMOS offers the same familiar speeds of HC HCMOS ICs with a 5 V supply. This allows 3.3 V ±0.3 V systems to be designed with the same speed and performance as 5 V ±10% systems using HCMOS HC ICs. The tremendous advantage of using

LV-HCMOS, considerably lower power consumption, is clearly shown in Fig.5. With a 3 V supply at 30 MHz, an LV-HCMOS octal transceiver consumes 70% less power than a similar advanced CMOS device. At lower supply voltages, the power savings are even greater.

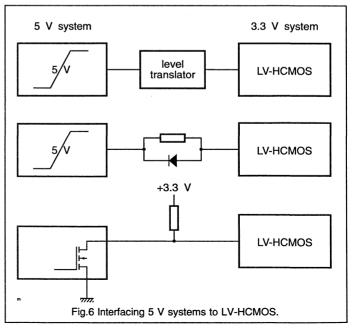

# INTERFACING IN MIXED 3 V / 5 V SYSTEMS

CMOS ICs like HLL and LV-CMOS have considerable benefits with respect to noise margins because,

unlike with bipolar ICs, there is hardly any voltage drop across the output devices. This means that the outputs swing virtually between the power supply rails, thereby allowing direct interfacing with TTL switching levels.

When interfacing HLL or LV-HCMOS outputs with standard TTL-compatible level logic inputs, the outputs of HLL and LV-HCMOS are adequate to directly drive the 5 V logic. When driving CMOS level devices (such as AC or HC) the output voltage of

HLL and LV-HCMOS is insufficient to ensure reliable operation. This problem can be easily resolved by using TTL-compatible HCMOS ICs (ACT or HCT) at the interface.

Since HLL inputs can withstand higher levels than the supply voltage, they can be directly connected to 5 V CMOS logic outputs.

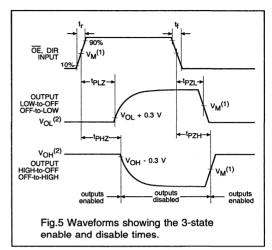

LV-HCMOS devices have a

protection diode between the input and V<sub>CC</sub>. This implies that the maximum input voltage is limited to  $V_{CC} + 0.5 V$ . When LV-HCMOS is driven by 5 V outputs having a TTL (totem-pole) compatible output voltage swing of about 3 V, direct drive is possible. However, when full 5 V output voltage swing devices are used, such as CMOS ASICs or CMOS logic, problems may occur. In such case a simple resistor-diode network or the use of open drain devices can provide a solution (see Fig. 6). Alternatively, HLL ICs can be used as 5 V/3 V level converters for connecting 5 V CMOS logic outputs to LV-HCMOS inputs.

# PHILIPS FOR ADVANCED LOGIC ICs

Our two new low-voltage CMOS logic families LV-HCMOS and HLL are only a small part of Philips' total portfolio which includes a wide range of advanced bipolar, CMOS and QUBIC (BiCMOS) logic ICs.

Continuity of supply from Philips is assured, thanks to our own global manufacturing/distribution organization, and to our alternate sourcing agreements for many products.

Philips' wafer fabrication plants and IC assembly factories are located close to market centres throughout the world. The continual extension of these facilities clearly demonstrates that Philips operates on a global scale, and is

committed to growth in virtually all countries. Ship-to-stock arrangements and Self-Qual programmes (which provide information about qualification activities for new/changed products/processes) are just two of the special customer services we can offer. Naturally, we also offer design-in support and technical assistance. Since Philips' technical expertise embraces a broad spectrum of application areas, we can offer you invaluable help with your product designs. Maintaining a close and open relationship with our customers helps us to optimize our design-ins.

# QUALITY AND RELIABILITY OF PHILIPS' PRODUCTS

All Philips' products are of a high quality, constantly enhanced by a system of continuous quality improvement. We start to achieve our high level of quality during development of new devices by including staff from our Quality Department in the development teams. Testing includes life testing (including HAST) and thermal shock. We use sound methods of

managing product reliability improvement to ensure that our products continue to perform to their specifications. Up-to-date quality reports are available to customers.

Over the years, Philips has proved itself to be a reliable supplier and our commitment to quality has been underlined by the many awards received in honour of outstanding achievements in this field. These awards include:

- The ISO 9001 qualification

- Qualified supplier to Hewlett Packard, Bosch, Canon, Chrysler, Delco, IBM cat. I & II and others

- The Ford Q1 award with consistently high scores

- The Bull Quality Award 1991

- Siemens' 'Best IC supplier' of 1989

- · Unisys Oscar 1990.

More specific information about Philips' Quality Programme can be found in the chapter on Quality on page 17.

# **Numerical index**

| 74HLL | family |

|-------|--------|

|-------|--------|

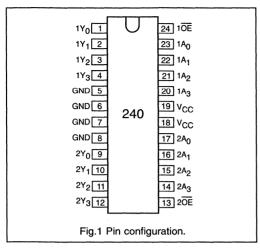

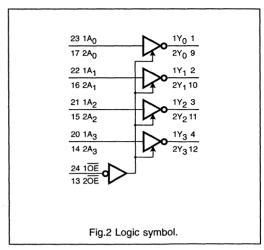

| 74HL33240 | Octal buffer/line driver; 3-state; inverting                      | 32  |

|-----------|-------------------------------------------------------------------|-----|

| 74HL33241 | Octal buffer/line driver; 3-state                                 | 36  |

| 74HL33244 | Octal buffer/line driver; 3-state                                 | 40  |

| 74HL33245 | Octal transceiver with directionpin; 3-state                      | 44  |

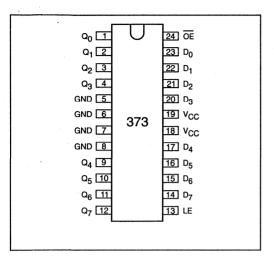

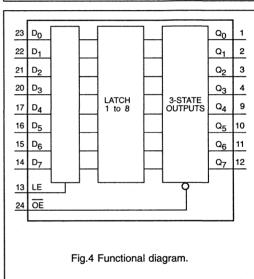

| 74HL33373 | Octal D-type transparent latch; 3-state                           | 48  |

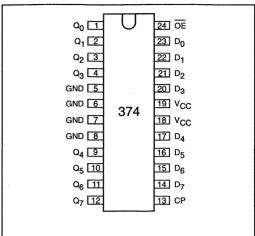

| 74HL33374 | Octal D-type flip-flop; positive edge-trigger; 3-state            | 52  |

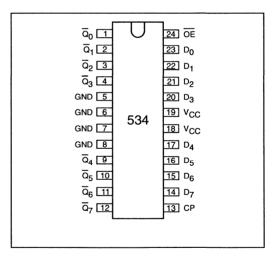

| 74HL33533 | Octal D-type transparent latch; 3-state; inverting                | 56  |

| 74HL33534 | Octal D-type flip-flop; positive edge-trigger; 3-state; inverting | 60  |

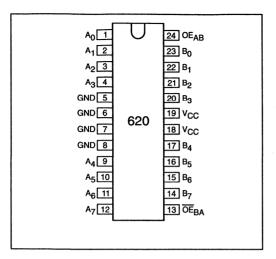

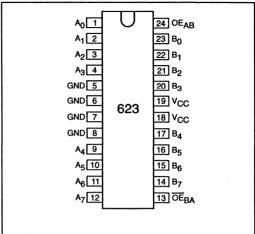

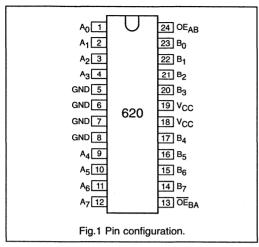

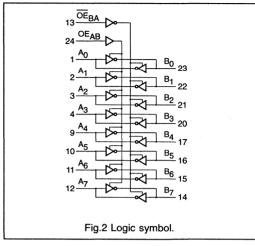

| 74HL33620 | Octal transceiver with dual enable; 3-state; inverting            | 64  |

| 74HL33623 | Octal transceiver with dual enable; 3-state                       | 68  |

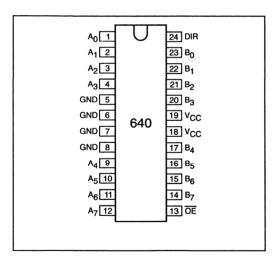

| 74HL33640 | Octal transceiver with direction pin; 3-state; inverting          | 72  |

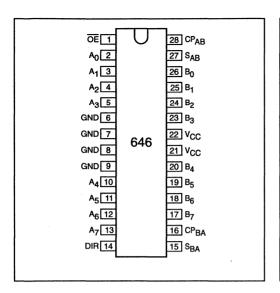

| 74HL33646 | Octal bus transceiver/register; 3-state                           | 76  |

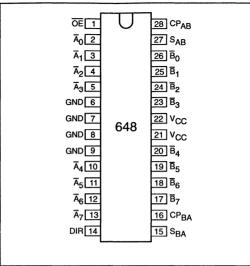

| 74HL33648 | Octal bus transceiver/register; 3-state; inverting                | 84  |

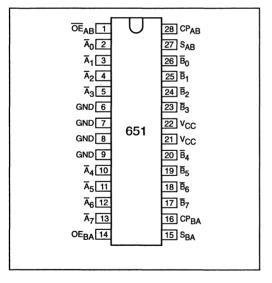

| 74HL33651 | Octal transceiver/register with dual enable; 3-state; inverting   | 92  |

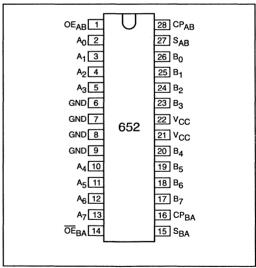

| 74HL33652 | Octal transceiver/register with dual enable: 3-state              | 100 |

# LV-HCMOS family

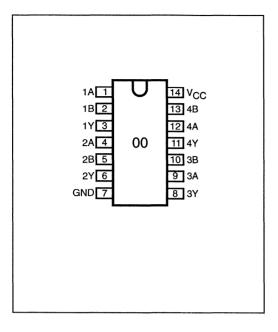

| 74LV00   | Quad 2-Input NAND gate                                          | 108 |

|----------|-----------------------------------------------------------------|-----|

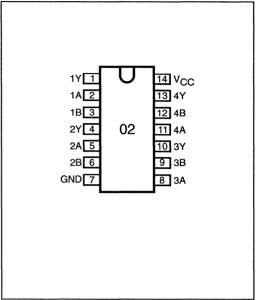

| 74LV02   | Quad 2-Input NOR gate                                           | 112 |

| 74LV04   | Hex Inverter                                                    | 116 |

| 74LVU04  | Hex Inverter (unbuffered)                                       | 120 |

| 74LV08   | Quad 2-Input AND gate                                           | 124 |

| 74LV14   | Hex Inverter Schmitt-trigger                                    | 128 |

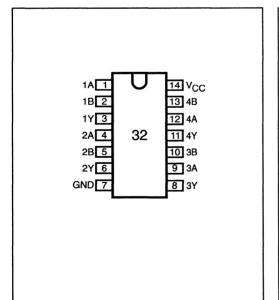

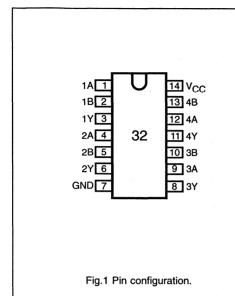

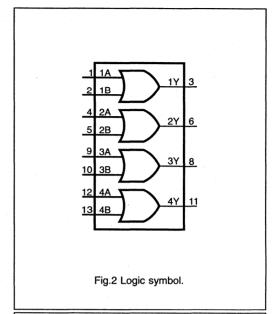

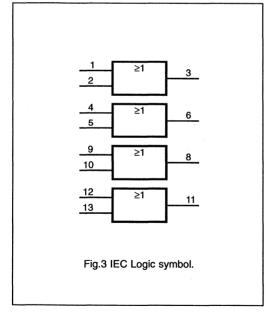

| 74LV32   | Quad 2-Input OR gate                                            | 132 |

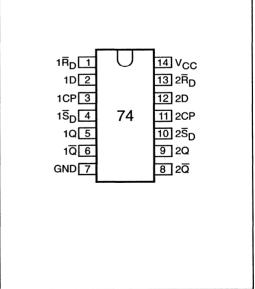

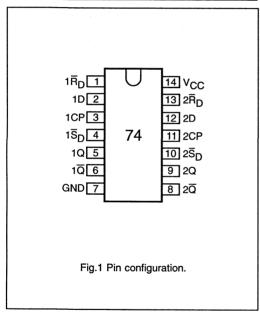

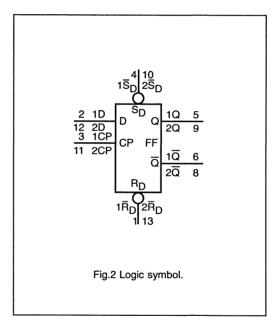

| 74LV74   | Dual D-type flip-flop with set and reset; positive edge-trigger | 136 |

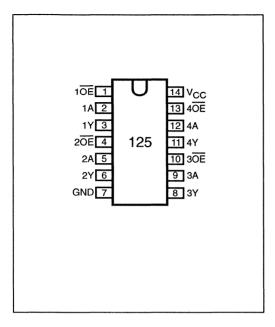

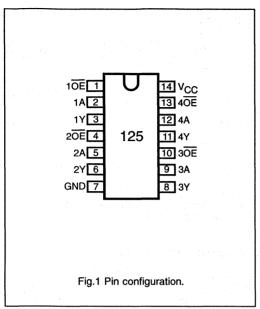

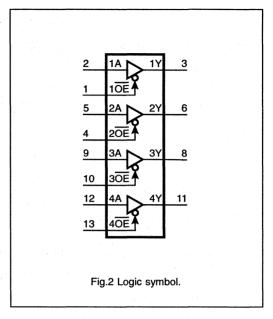

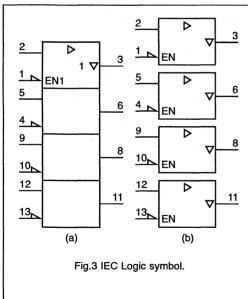

| 74LV125  | Quad buffer/line driver; 3-state                                | 142 |

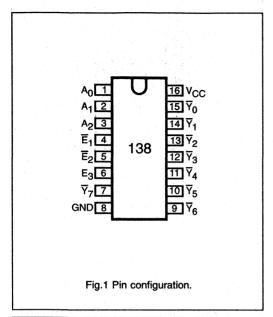

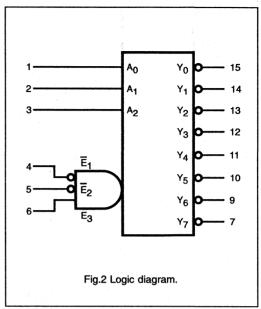

| 74LV138  | 3-to-8 line decoder/demultiplexer; inverting                    | 145 |

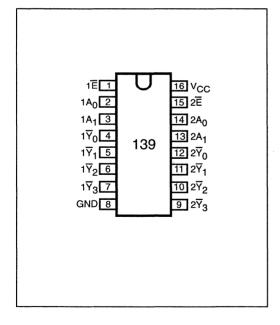

| 74LV139  | Dual 2-to-4 line decoder/demultiplexer                          | 150 |

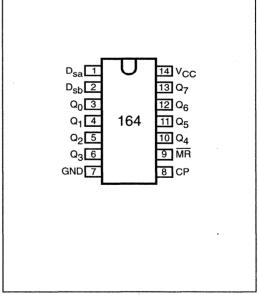

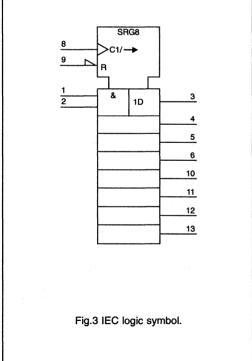

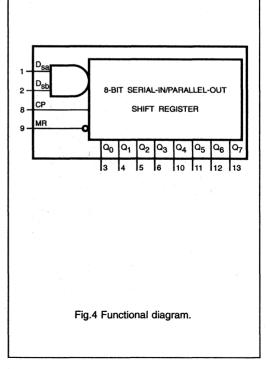

| 74LV164  | 8-bit serial-in/parallel-out shift register                     | 154 |

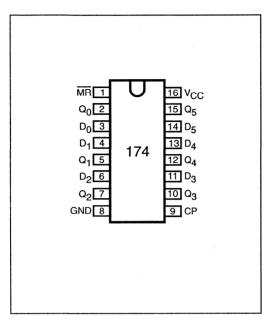

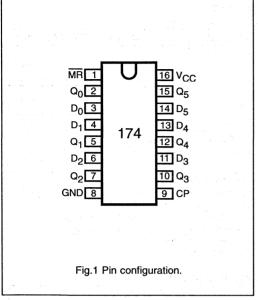

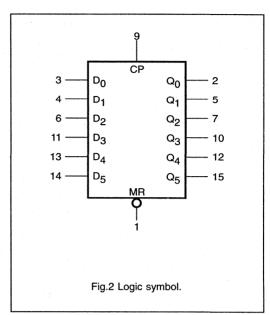

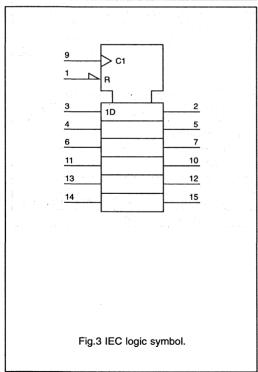

| 74LV174  | Hex D-type flip-flop with reset; positive edge-trigger          | 158 |

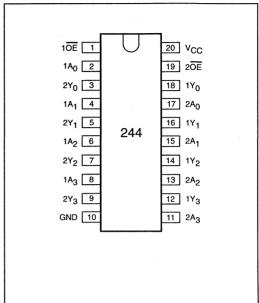

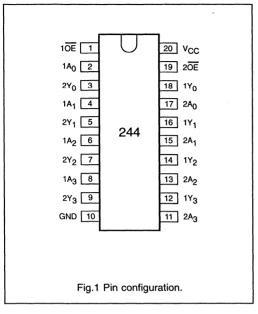

| 74LV244  | Octal buffer/line driver; 3-state                               | 162 |

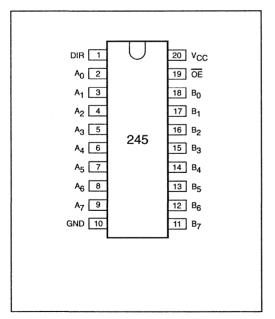

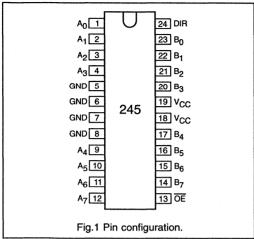

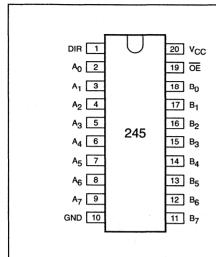

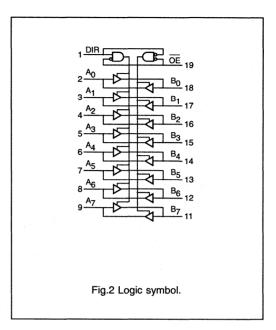

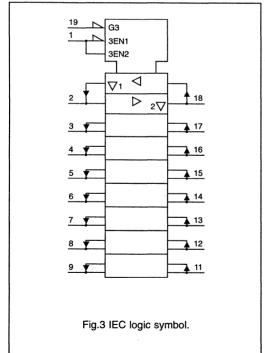

| 74LV245  | Octal bus transceiver; 3-state                                  | 166 |

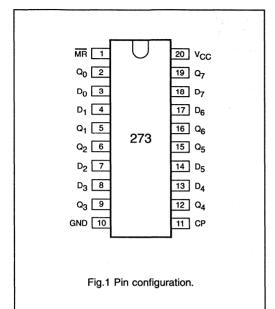

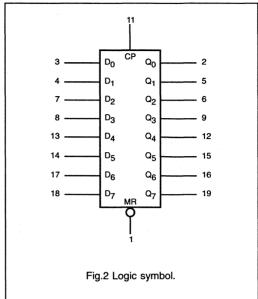

| 74LV273  | Octal D-type flip-flop with reset; positive edge-trigger        | 170 |

| 74LV373  | Octal D-type transparent latch; 3-state                         | 174 |

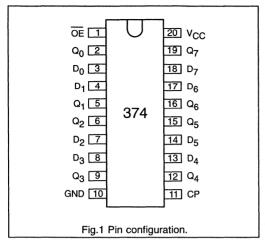

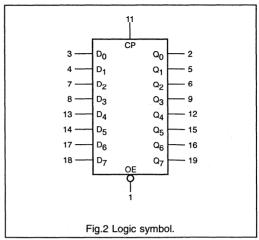

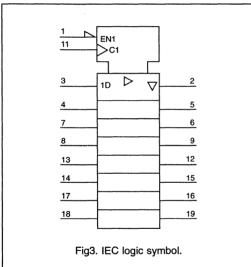

| 74LV374  | Octal D-type flip-flop; positive edge-trigger; 3-state          | 178 |

| 74LV573  | Octal D-type transparent latch; 3-state                         | 182 |

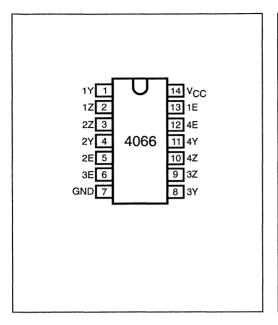

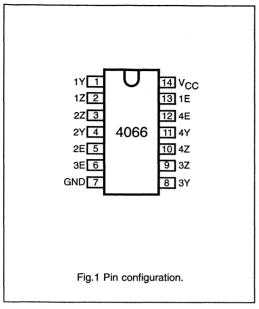

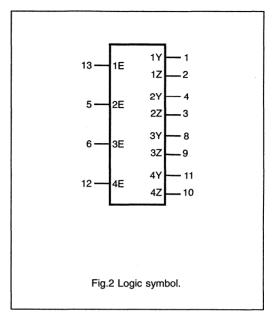

| 74LV4066 | Quad bilateral switches                                         | 186 |

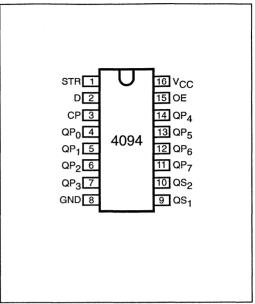

| 74LV4094 | 8-stage shift-and-store bus register                            | 190 |

|          |                                                                 |     |

8

August 1992

# **Ordering Information**

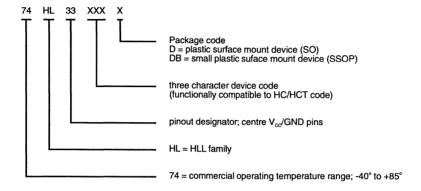

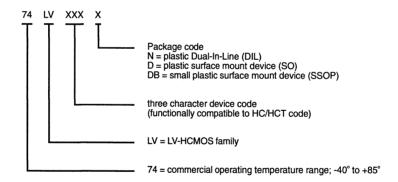

#### TYPE NUMBER DESIGNATIONS

#### **HLL RANGE**

#### **LV RANGE**

# **HLL family characteristics**

# **Family specifications**

#### **FAMILY DESCRIPTION**

The HLL family comprises extremely fast low-power logic ICs fabricated in a sub-micron CMOS process with two-level metal and epitaxial substrates. HLL ICs with 3.3 V  $\pm$ 0.3 V supply operates at twice the speed of FAST bipolar

logic and consumes only a fraction of the power. The HLL functions with supply voltages down to 1.2 V. The reduction from the conventional 5.0 V to 3.3 V reduces the output swing dramatically and this with the

low-inductance multiple centre power and ground pins significantly reduces noise and ground bounce that would otherwise occur for signals with this very high speed.

## RECOMMENDED OPERATING CONDITIONS FOR THE HLL FAMILY

| SYMBOL                          | PARAMETER                                        | MIN. | MAX.            | UNIT     | CONDITIONS                                         |

|---------------------------------|--------------------------------------------------|------|-----------------|----------|----------------------------------------------------|

| v <sub>cc</sub>                 | DC supply voltage (for max. speed performance)   | 3.0  | 3.6             | V        |                                                    |

| v <sub>cc</sub>                 | DC supply voltage (for low-voltage applications) | 1.2  | 3.6             | V        |                                                    |

| V <sub>i</sub>                  | DC input voltage range                           | 0    | 5.5             | V        |                                                    |

| V <sub>I/O</sub>                | DC input voltage range for I/Os                  | 0    | V <sub>cc</sub> | ٧        |                                                    |

| v <sub>o</sub>                  | DC output voltage range                          | 0    | V <sub>cc</sub> | ٧        |                                                    |

| T <sub>amb</sub>                | operating ambient temperature range in free air  | -40  | +85             | °C       | see DC and AC characteristics per device           |

| t <sub>r</sub> , t <sub>f</sub> | input rise and fall times                        | -    | 20<br>50        | ns<br>ns | V <sub>CC</sub> = 3.6 V<br>V <sub>CC</sub> = 1.2 V |

#### LIMITING VALUES FOR THE HLL FAMILY

In accordance with the Absolute Maximum Rating System (IEC 134) Voltages are referenced to GND (ground = 0 V)

| SYMBOL                             | PARAMETER                                                 | MIN. | MAX.                  | UNIT | CONDITIONS                                      |

|------------------------------------|-----------------------------------------------------------|------|-----------------------|------|-------------------------------------------------|

| V <sub>cc</sub>                    | DC supply voltage                                         | -0.5 | +4.6                  | ٧    |                                                 |

| I <sub>IK</sub>                    | DC input diode current                                    | _    | -50                   | mA   | V <sub>1</sub> < 0                              |

| V <sub>i</sub>                     | DC input voltage                                          | -0.5 | +5.5                  | ٧    | note 2                                          |

| V <sub>I/O</sub>                   | DC input voltage range for I/Os                           | -0.5 | V <sub>CC</sub> + 0.5 | ٧    |                                                 |

| I <sub>OK</sub>                    | DC output diode current                                   | -    | ±75                   | mA   | $V_O > V_{CC}$ or $V_O < 0$                     |

| V <sub>o</sub>                     | DC output voltage                                         | -0.5 | V <sub>CC</sub> + 0.5 | V    | note 2                                          |

| Io                                 | DC output source or sink current                          | -    | ±70                   | mA   | $V_O = 0$ to $V_{CC}$                           |

| I <sub>GND</sub> , I <sub>CC</sub> | DC V <sub>CC</sub> or GND current                         | _    | 100                   | mA   |                                                 |

| T <sub>stg</sub>                   | storage temperature range                                 | -60  | +150                  | °C   |                                                 |

| P <sub>tot</sub>                   | power dissipation per package<br>- plastic mini-pack (SO) | _    | 500                   | mW   | above + 70 °C<br>derate linearly with<br>8 mW/K |

#### Notes to the limiting values

- Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operating of the device at these or any other conditions beyond

- those under 'recommended operating conditions' is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

- The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

## DC CHARACTERISTICS FOR THE HLL FAMILY

Over recommended operating conditions

Voltages are referenced to GND (ground = 0 V)

|                 |                                     |                                                |                 | T <sub>amb</sub> (°C | <del>)</del>                                   |            | TEST CONDITIONS |                  |                                          |                                                     |

|-----------------|-------------------------------------|------------------------------------------------|-----------------|----------------------|------------------------------------------------|------------|-----------------|------------------|------------------------------------------|-----------------------------------------------------|

| SYMBOL          | PARAMETER                           |                                                | +25             |                      | -40 to                                         | +85        | UNIT            | V <sub>cc</sub>  | \ \ \                                    | OTHER                                               |

|                 |                                     | MIN.                                           | TYP.            | MAX.                 | MIN.                                           | MAX.       |                 | (V)              | V,                                       | OTHER                                               |

| V <sub>IH</sub> | HIGH level input voltage            | _                                              | -               | -                    | 2.0                                            | -          | ٧               | 3.6              |                                          |                                                     |

| V <sub>IL</sub> | LOW level input voltage             | _                                              | -               | _                    | _                                              | 0.8        | ٧               | 3.0              |                                          |                                                     |

| V <sub>H</sub>  | hysteresis (all inputs)             | _                                              | 0.25            | _                    | _                                              | _          | ٧               | 3.0<br>to<br>3.6 |                                          |                                                     |

| V <sub>OH</sub> | HIGH level output<br>voltage        | V <sub>CC</sub> - 0.2<br>V <sub>CC</sub> - 0.4 | v <sub>cc</sub> | -                    | V <sub>CC</sub> - 0.2<br>V <sub>CC</sub> - 0.4 | -          | ٧               | 3.0              | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = -100 μA<br>I <sub>O</sub> = -24 mA |

| V <sub>OL</sub> | LOW level output voltage            | _                                              | _               | 0.2<br>0.4           | -<br>-                                         | 0.2<br>0.4 | ٧               | 3.0              | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 100 μA<br>I <sub>O</sub> = 24 mA   |

| l <sub>1</sub>  | input leakage current               | _                                              | -               | _                    | <u>-</u>                                       | ±5         | μА              | 3.6              | V <sub>CC</sub><br>or<br>GND             |                                                     |

| l <sub>oz</sub> | 3-state output<br>OFF-state current | _                                              | _               | _                    | _                                              | 10         | μА              | 3.6              | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | V <sub>O</sub> = V <sub>CC</sub> or<br>GND          |

| I <sub>cc</sub> | quiescent supply current            | _                                              | _               | 8.0                  | _                                              | 80         | μА              | 3.6              | V <sub>CC</sub><br>or<br>GND             | I <sub>O</sub> = 0                                  |

# LV-HCMOS family characteristics

# Family specifications

#### The LV-HCMOS family

Please note that there is only one LV-HCMOS family and all the ICs are suitable for operation over the temperature range —40 °C to +125 °C.

However, as a reference for system designers, and to facilitate comparison with other logic families, the performance of LV-HCMOS ICs is specified at 25 °C and over the temperature ranges –40 °C to +85 °C and –40 °C to +125 °C.

## RECOMMENDED OPERATING CONDITIONS FOR THE LV-HCMOS FAMILY

| SYMBOL                          | PARAMETER                                                      | MIN.             | TYP.     | MAX.                      | UNIT | CONDITIONS                                                                                               |

|---------------------------------|----------------------------------------------------------------|------------------|----------|---------------------------|------|----------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub>                 | DC supply voltage                                              | 1.2              | 3.3      | 3.6                       | ٧    |                                                                                                          |

| V <sub>I</sub>                  | input voltage                                                  | 0                | _        | V <sub>cc</sub>           | ٧    |                                                                                                          |

| V <sub>o</sub>                  | output voltage                                                 | 0                | -        | V <sub>cc</sub>           | ٧    |                                                                                                          |

| T <sub>amb</sub>                | operating ambient temperature range in free air                | -40<br>-40       | -        | +85<br>+125               | °C   | see DC and AC characteristics per device                                                                 |

| t <sub>r</sub> , t <sub>f</sub> | input rise and fall times except for<br>Schmitt-trigger inputs | _<br>_<br>_<br>_ | - '.<br> | 1000<br>700<br>500<br>400 | ns   | V <sub>CC</sub> = 1.2 V<br>V <sub>CC</sub> = 2.0 V<br>V <sub>CC</sub> = 3.0 V<br>V <sub>CC</sub> = 3.6 V |

#### ABSOLUTE MAXIMUM RATINGS FOR THE LV-HCMOS FAMILY

Limiting values in accordance with the Absolute Maximum Rating System (IEC 134). Voltages are referenced to GND (ground = 0 V).

| SYMBOL                                  | PARAMETER                                                                             | MIN.     | MAX.     | UNIT | CONDITIONS                                                            |

|-----------------------------------------|---------------------------------------------------------------------------------------|----------|----------|------|-----------------------------------------------------------------------|

| V <sub>cc</sub>                         | DC supply voltage                                                                     | -0.5     | +5.0     | ٧    |                                                                       |

| ±I <sub>IK</sub>                        | DC input diode current                                                                | _        | 20       | mA   | $V_{\rm I} < -0.5 \text{ or } V_{\rm I} > V_{\rm CC} +0.5 \text{ V}$  |

| ±I <sub>OK</sub>                        | DC output diode current                                                               | -        | 50       | mA   | $V_{\rm O} < -0.5 \text{ or } V_{\rm O} > V_{\rm CC} + 0.5 \text{ V}$ |

| ±I <sub>O</sub>                         | DC output source or sink current - standard outputs - bus driver outputs              | <u> </u> | 25<br>35 | mA   | -0.5 V < V <sub>O</sub> < V <sub>CC</sub> + 0.5 V                     |

| ±I <sub>GND</sub> ,<br>±I <sub>CC</sub> | DC $V_{\rm CC}$ or GND current for types with - standard outputs - bus driver outputs | -        | 50<br>70 | mA   |                                                                       |

| T <sub>stg</sub>                        | storage temperature range                                                             | -65      | +150     | °C   |                                                                       |

|                                         | power dissipation per package                                                         |          |          |      | for temperature range: -40 to +125 °C                                 |

| P <sub>tot</sub>                        | - plastic DIL                                                                         | -        | 750      | mW   | above + 70 °C derate linearly with 12 mW/K                            |

|                                         | - plastic mini-pack (SO)                                                              | _        | 500      | mW   | above + 70 °C derate linearly with 8 mW/K                             |

## Notes to the limiting values

- Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operating of the device at these or any other conditions beyond

- those under 'recommended operating conditions' is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

- The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

## DC CHARACTERISTICS FOR THE LV-HCMOS FAMILY

Over recommended operating conditions

Voltages are referenced to GND (ground = 0 V)

|                 |                                                          |                   |                   |                   | Γ <sub>amb</sub> (° | C)                   |                   |                       | TEST CONDITI |                   |                                          |                                            |  |

|-----------------|----------------------------------------------------------|-------------------|-------------------|-------------------|---------------------|----------------------|-------------------|-----------------------|--------------|-------------------|------------------------------------------|--------------------------------------------|--|

| SYMBOL          | PARAMETER                                                |                   | +25               |                   | -40 t               | o +85                | -40 t             | o +125                | UNIT         | V <sub>C</sub>    |                                          | OTUED                                      |  |

|                 |                                                          | MIN.              | TYP.              | MAX.              | MIN.                | MAX.                 | MIN.              | MAX.                  |              | (v)               | V                                        | OTHER                                      |  |

| V <sub>IH</sub> | HIGH level input voltage                                 | 0.9<br>1.4<br>2.1 | -                 |                   | 0.9<br>1.4<br>2.1   | -<br>-               | 0.9<br>1.4<br>2.1 |                       | ٧            | 1.2<br>2.0<br>3.0 |                                          |                                            |  |

| V <sub>IL</sub> | LOW level input voltage                                  | -<br>-            |                   | 0.3<br>0.6<br>0.9 | -<br>-<br>-         | 0.3<br>0.6<br>0.9    | -<br>-<br>-       | 0.3<br>0.6<br>0.9     | ٧            | 1.2<br>2.0<br>3.0 |                                          |                                            |  |

| V <sub>OH</sub> | HIGH level output<br>voltage; all<br>outputs             | 1.1<br>1.9<br>2.9 | 1.2<br>2.0<br>3.0 | 7 <u>-</u> 1      | 1.0<br>1.9<br>2.9   | -<br>-<br>-          | 1.0<br>1.9<br>2.9 | -<br>-<br>-           | v            | 1.2<br>2.0<br>3.0 | or                                       | -l <sub>O</sub> = 50 μA                    |  |

| V <sub>OH</sub> | HIGH level output voltage; standard outputs              | 2.48              | 2.82              | -                 | 2.34                | -                    | 2.20              | _                     | ٧            | 3.0               | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | -I <sub>O</sub> = 6 mA                     |  |

| V <sub>OH</sub> | HIGH level output<br>voltage; bus<br>driver outputs      | 2.48              | 2.82              |                   | 2.34                | -                    | 2.20              | _                     | ٧            | 3.0               | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | -I <sub>O</sub> = 8 mA                     |  |

| V <sub>OL</sub> | LOW level output<br>voltage; all<br>outputs              | -<br>-<br>-       | 0<br>0<br>0       | 0.1<br>0.1<br>0.1 | -<br>-              | 0.1<br>0.1<br>0.1    | -<br>-<br>-       | 0.1<br>0.1<br>0.1     | ٧            |                   | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 50 μA                     |  |

| V <sub>OL</sub> | LOW level output voltage; standard outputs               | -                 | 0.25              | 0.33              | _                   | 0.4                  | -                 | 0.5                   | ٧            |                   | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 6 mA                      |  |

| V <sub>OL</sub> | LOW level output<br>voltage; bus<br>driver outputs       | _                 | 0.20              | 0.33              | _                   | 0.4                  | _                 | 0.5                   | ٧            | 3.0               | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 8 mA                      |  |

| l <sub>1</sub>  | input leakage<br>current                                 | -                 | _                 | 0.1               | _                   | 1.0                  | -                 | 1.0                   | μА           | 3.6               | V <sub>CC</sub><br>or<br>GND             |                                            |  |

| l <sub>oz</sub> | 3-state output<br>OFF-state current                      | _                 |                   | 0.5               | - T                 | 5.0                  | _                 | 10.0                  | μА           | 3.6               | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | V <sub>O</sub> = V <sub>CC</sub> or<br>GND |  |

| I <sub>cc</sub> | quiescent supply<br>current;<br>SSI<br>flip-flops<br>MSI | -<br>-<br>-       | -<br>-<br>-       | 2.0<br>4.0<br>8.0 | -<br>-<br>-         | 20.0<br>40.0<br>80.0 |                   | 40.0<br>80.0<br>160.0 | μА           | 3.6               | V <sub>CC</sub><br>or<br>GND             | I <sub>O</sub> = 0                         |  |

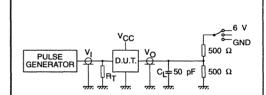

## AC OUTPUT CHARACTERISTICS FOR THE LV-HCMOS FAMILY

|                                                       |                                      |      |      |      | Γ <sub>amb</sub> (° |      | T           | TEST CONDITIONS |      |                |           |

|-------------------------------------------------------|--------------------------------------|------|------|------|---------------------|------|-------------|-----------------|------|----------------|-----------|

| SYMBOL                                                | PARAMETER                            | +25  |      |      | -40 to +85          |      | -40 to +125 |                 | UNIT | V <sub>C</sub> | WAVEFORMS |

|                                                       |                                      | MIN. | TYP. | MAX. | MIN.                | MAX. | MIN.        | MAX.            |      | (v)            | WAVEFORMS |

|                                                       | Augustain — Airean                   | -    | 35   | _    | _                   | -    | _           | _               |      | 1.2            |           |

| $t_{THL}/t_{TLH}$                                     | transition time;<br>standard outputs | -    | 10   | 20   | -                   | 25   | - 7         | 30              | ns   | 2.0            |           |

|                                                       | standard outputs                     | -    | 7    | 15   | -                   | 19   | -           | 23              |      | 3.0            |           |

|                                                       | transition time;                     | -    | 25   | -    | 7 -                 | _    | _           | -               |      | 1.2            |           |

| t <sub>THL</sub> /t <sub>TLH</sub> bus driver outputs | · -                                  | 8    | 16   | _    | 20                  | -    | 24          | ns              | 2.0  |                |           |

|                                                       | bus ariver outputs                   | _    | 5    | 10   | -                   | 13   | 1-          | 15              |      | 3.0            |           |

#### **DEFINITIONS OF SYMBOLS AND TERMS USED IN DATA SHEETS**

#### Currents

Positive current is defined as conventional current flow into a device. Negative current is defined as conventional current flow out of a device.

| I <sub>cc</sub>  | Quiescent power supply current; the current flowing into the V <sub>CC</sub> supply terminal.                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Δl <sub>CC</sub> | Additional quiescent supply current per input pin at a specified input voltage and V <sub>CC</sub> .                                                             |

| I <sub>GND</sub> | Quiescent power supply current; the current flowing into the GND terminal.                                                                                       |

| l <sub>1</sub>   | Input leakage current; the current flowing into a device at a specified input voltage and V <sub>CC</sub> .                                                      |

| I <sub>IK</sub>  | Input diode current; the current flowing into a device at a specified input voltage.                                                                             |

| lo               | Output source or sink current; the current flowing into a device at a specified output voltage.                                                                  |

| I <sub>ok</sub>  | Output diode current; the current flowing into a device at a specified output voltage.                                                                           |

| l <sub>oz</sub>  | OFF-state output current: the leakage current flowing into the output of a 3-state device in the OFF-state, when the output is connected to $V_{\rm CC}$ or GND. |

| I <sub>S</sub>   | Analog switch leakage current; the current flowing into an analog switch at a specified voltage across the switch and $\rm V_{CC}$ .                             |

## **Voltages**

All voltages are referenced to GND (ground), which is typically 0 V.

|                  | 0 , 1                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND              | Supply voltage; for a device with a single negative power supply, the most negative power supply, used as the reference level for other voltages; typically ground.                               |

| V <sub>cc</sub>  | Supply voltage; the most positive potential on the device.                                                                                                                                        |

| V <sub>EE</sub>  | Supply voltage; the one of two (GND and V <sub>EE</sub> ) negative power supplies.                                                                                                                |

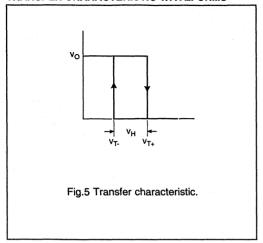

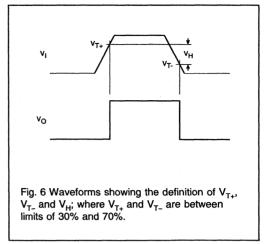

| V <sub>H</sub>   | Hysteresis voltage; difference between the trigger levels, when applying a positive and negative-going input signal.                                                                              |

| V <sub>I</sub>   | DC input voltage                                                                                                                                                                                  |

| V <sub>I/O</sub> | DC input voltage for I/Os                                                                                                                                                                         |

| V <sub>IH</sub>  | HIGH level input voltage; the range of input voltages that represents a logic HIGH level in the system.                                                                                           |

| V <sub>IL</sub>  | LOW level input voltage; the range of input voltages that represents a logic LOW level in the system.                                                                                             |

| V <sub>OH</sub>  | HIGH level output voltage; the range of voltages at an output terminal with a specified output loading and supply voltage. Device inputs are conditioned to establish a HIGH level at the output. |

| V <sub>OL</sub>  | LOW level output voltage; the range of voltages at an output terminal with a specified output loading and supply voltage. Device inputs are conditioned to establish a LOW level at the output.   |

| V <sub>T+</sub>  | Trigger threshold voltage; positive-going signal.                                                                                                                                                 |

| V <sub>T-</sub>  | Trigger threshold voltage; negative going signal.                                                                                                                                                 |

|                  |                                                                                                                                                                                                   |

August 1992 14

# HLL and LV-HCMOS family characteristics

Definitions of symbols

# Analog terms

| R <sub>ON</sub>  | ON-resistance; the effective ON-state resistance of an analog switch, at a specified voltage across the switch and output load.                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| ΔR <sub>ON</sub> | ΔΟΝ-resistance; the difference in ON-resistance between any two switches of an analog device at a specified voltage across the switch and output load. |

## Capacitances

| Cı               | Input capacitance; the capacitance measured at a terminal connected to an input of a device.                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>I/O</sub> | Input/Output capacitance; the capacitance measured at a terminal connected to an I/O-pin (e.g. a transceiver).                                                   |

| CL               | Output load capacitance; the capacitance connected to an output terminal including jig and probe capacitance.                                                    |

| C <sub>PD</sub>  | Power dissipation capacitance; the capacitance used to determine the dynamic power dissipation per logic function, when no extra load is provided to the device. |

| C <sub>s</sub>   | Switch capacitance; the capacitance of a terminal to a switch of an analog device.                                                                               |

# HLL and LV-HCMOS family characteristics

## AC switching parameters

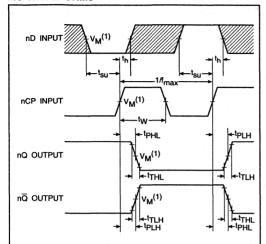

| f <sub>i</sub>                  | Input frequency; for combinatorial logic devices the maximum number of inputs and outputs switching in accordance with the device function table. For sequential logic devices the clock frequency using alternate HIGH and LOW for data input or using the toggle mode, whichever is applicable.                                                                                                                                                                         |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>o</sub>                  | Output frequency; each output.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

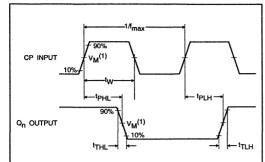

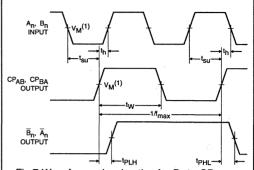

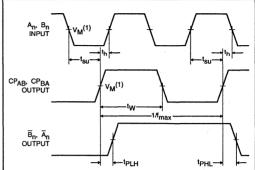

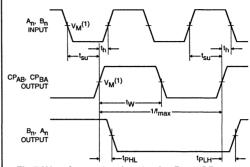

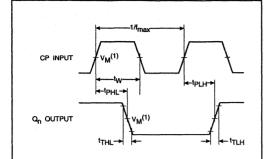

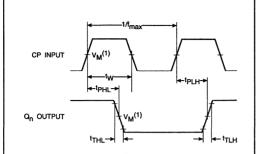

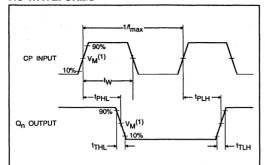

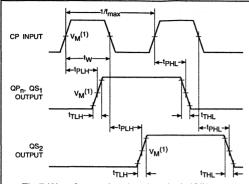

| f <sub>max</sub>                | Maximum clock frequency; clock input waveforms should have a 50% duty factor and be such as to cause the outputs to be switching from $10\%V_{CC}$ to $90\%V_{CC}$ in accordance with the device function table.                                                                                                                                                                                                                                                          |

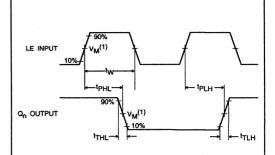

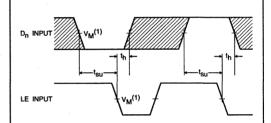

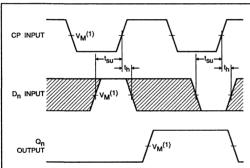

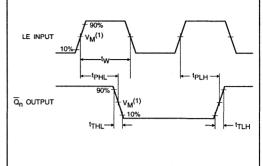

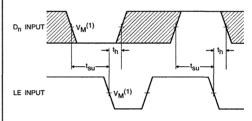

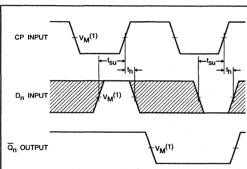

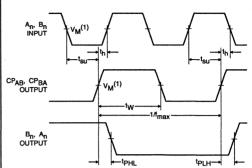

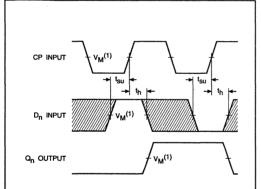

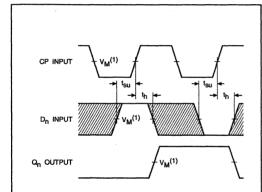

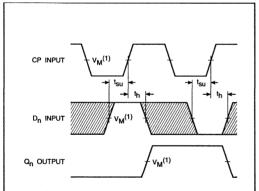

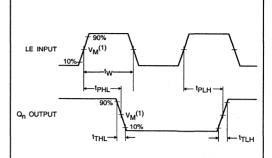

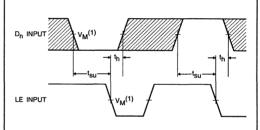

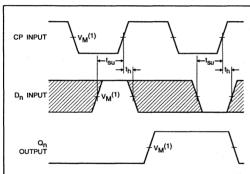

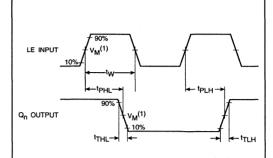

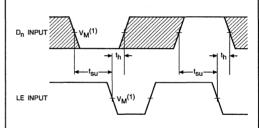

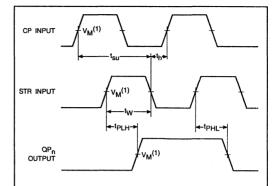

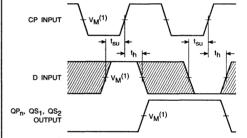

| t <sub>h</sub>                  | Hold time; the interval immediately following the active transition of the timing pulse (usually the clock pulse) or following the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure their continued recognition. A negative hold time indicates that the correct logic level may be released prior to the timing pulse and still be recognized.                           |

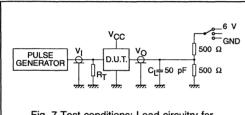

| t <sub>r</sub> , t <sub>r</sub> | Clock input rise and fall times; 10% and 90% values.                                                                                                                                                                                                                                                                                                                                                                                                                      |

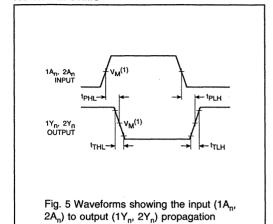

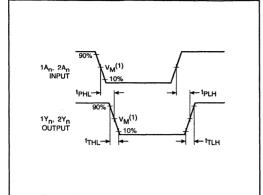

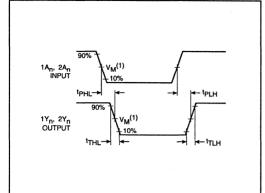

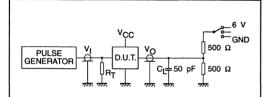

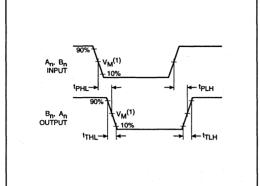

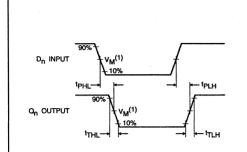

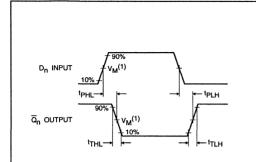

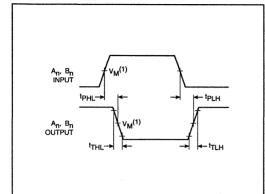

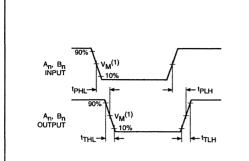

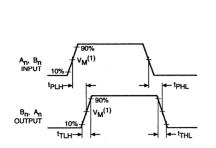

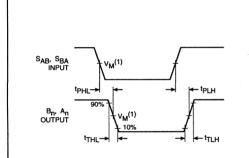

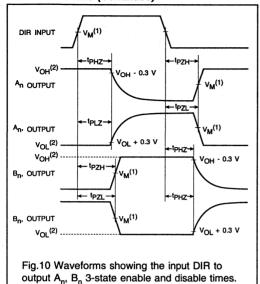

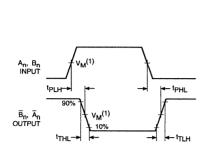

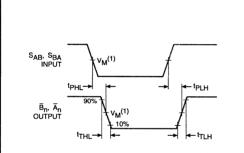

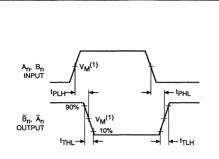

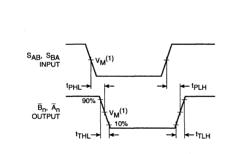

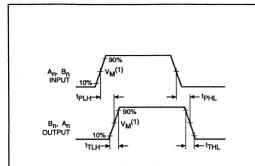

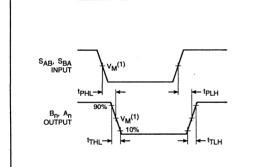

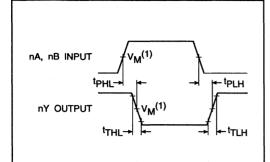

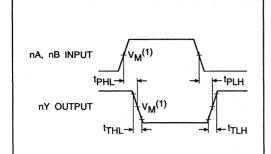

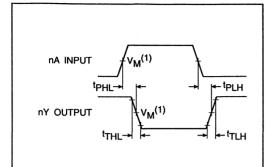

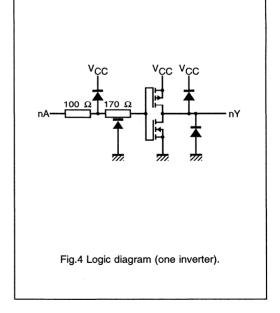

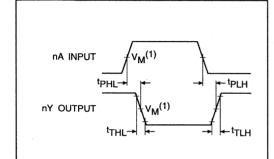

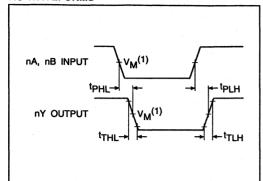

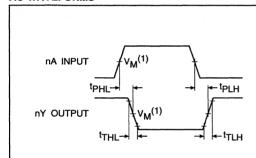

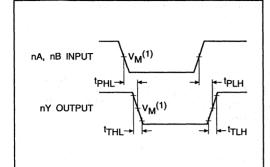

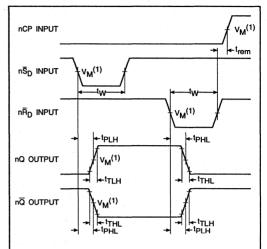

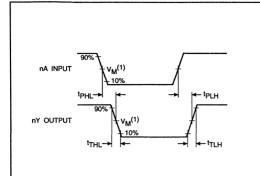

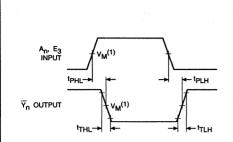

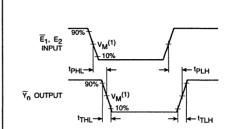

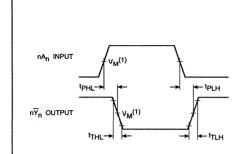

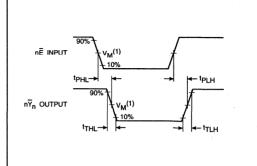

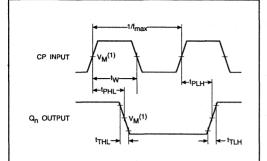

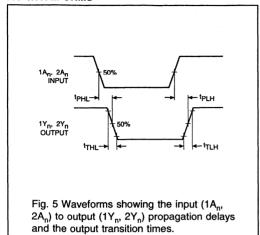

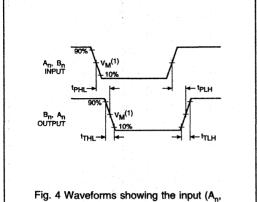

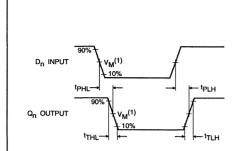

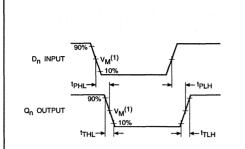

| t <sub>PHL</sub>                | Propagation delay; the time between the specified reference points, normally the 50% points for logic devices on the input and output waveforms, with the output changing from the defined HIGH level to the defined LOW level.                                                                                                                                                                                                                                           |

| t <sub>PLH</sub>                | Propagation delay; the time between the specified reference points, normally the 50% points for logic devices on the input and output waveforms, with the output changing from the defined LOW level to the defined HIGH level.                                                                                                                                                                                                                                           |

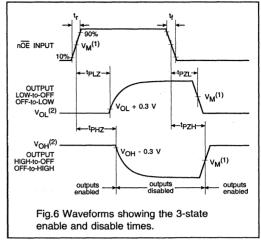

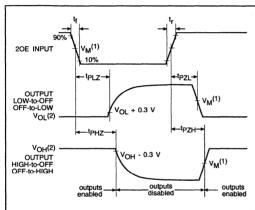

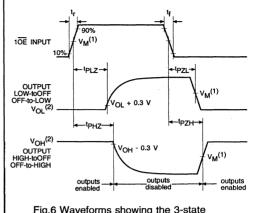

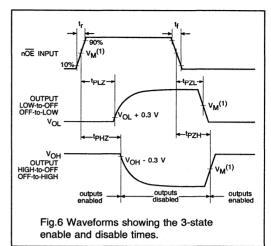

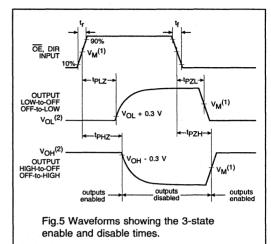

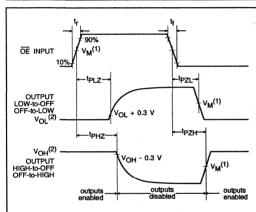

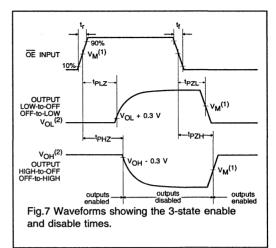

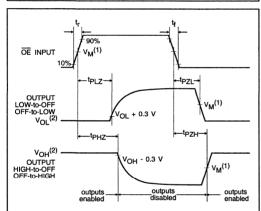

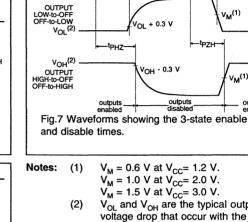

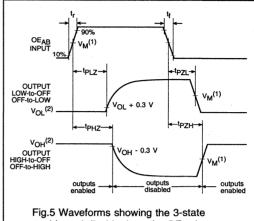

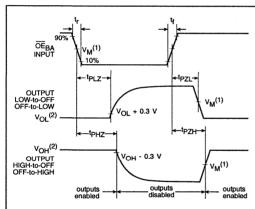

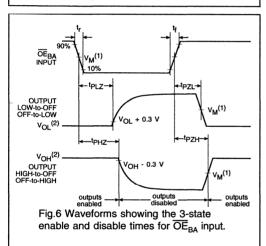

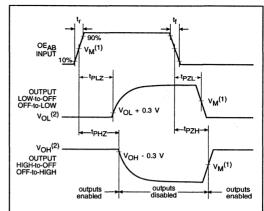

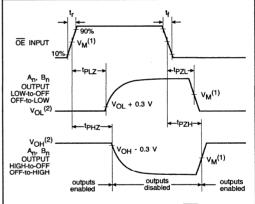

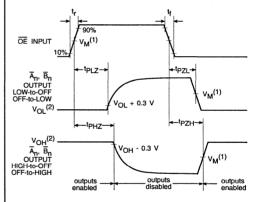

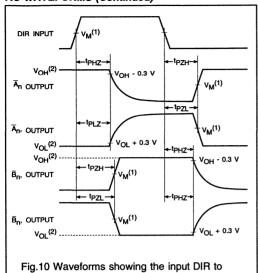

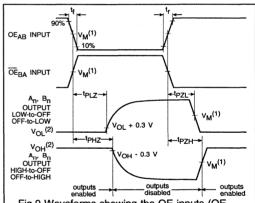

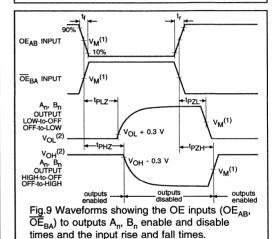

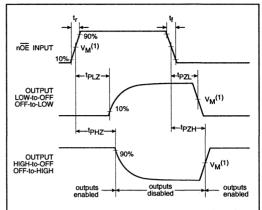

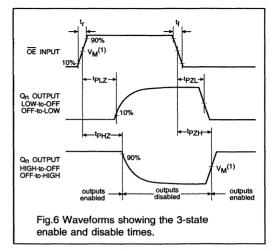

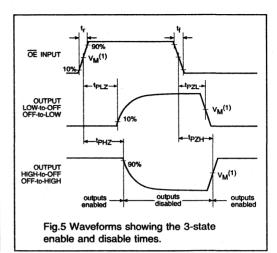

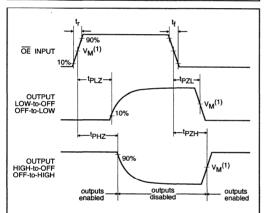

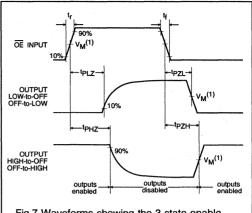

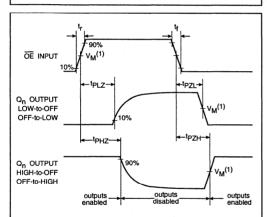

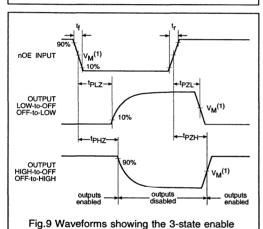

| t <sub>PHZ</sub>                | 3-state output disable time; the time between the specified reference points, normally the 50% points for the logic devices on the output enable input voltage waveform and a point representing 10% of the output swing on the output voltage waveform of a 3-state device, with the output changing from a HIGH level (V <sub>OH</sub> ) to a high impedance OFF-state (Z).                                                                                             |

| t <sub>PLZ</sub>                | 3-state output disable time; the time between the specified reference points, normally the 50% points for the logic devices on the output enable input voltage waveform and a point representing 10% of the output swing on the output voltage waveform of a 3-state device, with the output changing from a LOW level ( $V_{OL}$ ) to a high impedance OFF-state ( $Z$ ).                                                                                                |

| t <sub>PZH</sub>                | 3-state output enable time; the time between the specified reference points, normally the 50% points for the logic devices on the output enable input voltage waveform and the 50% point on the output voltage waveform of a 3-state device, with the output changing from a high impedance OFF-state (Z) to a HIGH level ( $V_{OH}$ ).                                                                                                                                   |

| t <sub>PZL</sub>                | 3-state output enable time; the time between the specified reference points, normally the 50% points for the logic devices on the output enable input voltage waveform and the 50% point on the output voltage waveform of a 3-state device, with the output changing from a high impedance OFF-state (Z) to a LOW level ( $V_{OL}$ ).                                                                                                                                    |

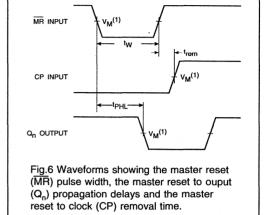

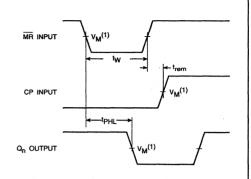

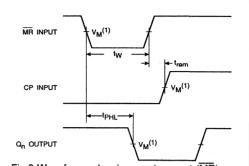

| t <sub>rem</sub>                | Removal time; the time between the end of an overriding asynchronous input, typically a clear or reset input, and the earliest permissible beginning of a synchronous control input, typically a clock input, normally measured at the 50% points for logic devices on both input voltage waveforms.                                                                                                                                                                      |

| t <sub>su</sub>                 | Set-up time; the interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure their recognition. A negative set-up time indicates that the correct logic level may be initiated sometime after the active transition of the timing pulse and still be recognized. |

| t <sub>THL</sub>                | Output transition time; the time between two specified reference points on a waveform, normally 90% and 10% points, that is changing from HIGH-to-LOW.                                                                                                                                                                                                                                                                                                                    |

| t <sub>TLH</sub>                | Output transition time; the time between two specified reference points on a waveform, normally 10% and 90% points, that is changing from LOW-to-HIGH.                                                                                                                                                                                                                                                                                                                    |

| t <sub>w</sub>                  | Pulse width; the time between the 50% amplitude points on the leading and trailing edges of a pulse for the logic family devices                                                                                                                                                                                                                                                                                                                                          |

16

August 1992

#### QUALITY AT PHILIPS SEMICONDUCTORS

#### **Total Quality Management**

Philips Semiconductors are a Quality Company, renowned for the high quality of our products and service. We keep alive this tradition by constantly aiming towards one ultimate standard, that of zero defects. This aim is guided by our Total Quality Management (TQM) system, the basis of which is:

#### QUALITY ASSURANCE

based on ISO 9000 standards, customer standards such as Ford Q1 and IBM MDQ, and the CECC system of conformity. Our factories are certified to ISO 9000 and CECC by external inspectorates

#### PARTNERSHIPS WITH CUSTOMERS

PPM co-operations, design-in agreements, and ship-to-stock, just-in-time and self-qualification programmes

#### PARTNERSHIPS WITH SUPPLIERS

ship-to-stock, statistical process control and ISO 9000 audits

#### QUALITY IMPROVEMENT PROGRAMME

continuous process and system improvement, design improvement, complete use of statistical process control, realization of our final objective of zero defects, and logistics improvement by ship-to-stock and just-in-time agreements.

#### Advanced quality planning

During the design and development of new products and processes, quality is built-in by advanced quality planning. Through failure-mode-and-effect analysis the critical parameters are detected and measures taken to ensure good performance on these

parameters. The capability of process steps is also planned in this phase.

#### **Product conformance**

The assurance of product conformance is an integral part of our quality assurance (QA) practice. This is achieved by:

- incoming material management through partnerships with suppliers

- in-line quality assurance to monitor process reproducibility during manufacture and initiate any necessary corrective action. Critical process steps are 100% under statistical process control

- acceptance tests on finished products to verify conformance with the device specification.

The test results are used for quality feedback and corrective actions. The inspection and test requirements are detailed in the general quality specifications

- periodic inspections to monitor and measure the conformance of products.

#### Product reliability

With the increasing complexity of OEM (original equipment manufacturer) equipment. component reliability must be extremely high. Our research laboratories and development departments study the failure mechanisms of semiconductors. Their studies have resulted in design rules and process optimization for the highest built-in product reliability. Highly accelerated tests are applied to the products reliability evaluation. Rejects from reliability tests and from customer complaints are submitted to failure analysis, to result in corrective action.

#### **Customer responses**

Our quality improvement depends on joint action with our customer. We need our customer's inputs and we invite constructive comments on all aspects of our performance. Please contact our local sales representative.

#### **RATING SYSTEMS**

The rating systems described are those recommended by the IEC in its publication number 134.

#### Definitions of terms used

#### ELECTRONIC DEVICE

An electronic tube or valve, transistor or other semiconductor device. This definition excludes inductors, capacitors, resistors and similar components.

#### CHARACTERISTIC

A characteristic is an inherent and measurable property of a device. Such a property may be electrical, mechanical, thermal, hydraulic, electro-magnetic or nuclear, and can be expressed as a value for stated or recognized conditions. A characteristic may also be a set of related values, usually shown in graphical form.

### BOGEY ELECTRONIC DEVICE

An electronic device whose characteristics have the published nominal values for the type. A bogey electronic device for any particular application can be obtained by considering only those characteristics that are directly related to the application.

#### **RATING**

A value that establishes either a limiting capability or a limiting condition for an electronic device. It is determined for specified values of environment and operation, and may be stated in

any suitable terms. Limiting conditions may be either maxima or minima.

#### RATING SYSTEM

The set of principles upon which ratings are established and which determine their interpretation. The rating system indicates the division of responsibility between the device manufacturer and the circuit designer, with the object of ensuring that the working conditions do not exceed the ratings.

# Absolute maximum rating system

Absolute maximum ratings are limiting values of operating and environmental conditions applicable to any electronic device of a specified type, as defined by its published data, which should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking no responsibility for equipment variations, environmental variations, and the effects of changes in operating conditions due to variations in the characteristics of the device under consideration and of all other electronic devices in the equipment.

The equipment manufacturer should design so that, initially and throughout the life of the device, no absolute maximum value for the intended service is exceeded with any device, under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, equipment control adjustment, load variations, signal variation, environmental conditions, and variations in characteristics of the device under consideration and of all other electronic devices in the equipment.

#### Design maximum rating system

Design maximum ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under the worst probable conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device, taking responsibility for the effects of changes in operating conditions due to variations in the characteristics of the electronic device under consideration.

The equipment manufacturer should design so that, initially and throughout the life of the device, no design maximum value for the intended service is exceeded with a bogey electronic device, under the worst probable operating conditions with respect to supply voltage variation, equipment component variation, variation in characteristics of all other devices in the equipment, load variation, signal variation and environmental conditions.

### Design centre rating system

Design centre ratings are limiting values of operating and environmental conditions applicable to a bogey electronic device of a specified type as defined by its published data, and should not be exceeded under normal conditions.

These values are chosen by the device manufacturer to provide acceptable serviceability of the device in average applications, taking responsibility for normal changes in operating conditions due to rated supply voltage variation, equipment component variation, equipment control adjustment, load variation, signal variation, environmental conditions,

and variations in the characteristics of all electronic devices.

The equipment manufacturer should design so that, initially, no design centre value for the intended service is exceeded with a bogey electronic device in equipment operating at the stated normal supply voltage.

## HANDLING MOS DEVICES

#### **Electrostatic charges**

Electrostatic charges can exist in many things: for example. man-made-fibre clothing, moving machinery, objects with air blowing across them, plastic storage bins, sheets of paper stored in plastic envelopes, paper from electrostatic copying machines, and people. The charges are caused by friction between two surfaces, at least one of which is non-conductive. The magnitude and polarity of the charges depend on the different affinities for electrons of the two materials rubbing together, the friction force and the humidity of the surrounding air.

Electrostatic discharge is the transfer of an electrostatic charge between bodies at different potentials and occurs with direct contact or when induced by an electrostatic field. All of our MOS devices are internally protected against electrostatic discharge but they **can** be damaged if the following precautions are not taken.

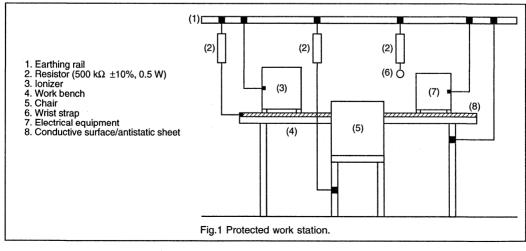

#### Work station

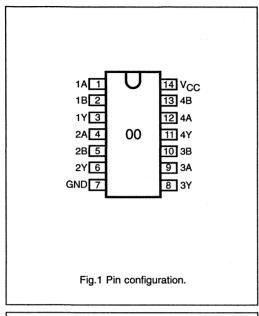

Fig.1 shows a working area suitable for safely handling electrostatic sensitive devices. It has a work bench, the surface of which is conductive or covered by an antistatic sheet. Typical resistivity for the bench surface is between 1 and 500 k $\Omega$ ; per cm<sup>2</sup>. The floor should also be covered with antistatic material.

The following precautions should be observed:

- persons at a work bench should be earthed via a wrist strap and a resistor

- all mains-powered electrical equipment should be connected via an earth leakage switch

- equipment cases should be earthed

- relative humidity should be maintained between 50 and 65%

- an ionizer should be used to neutralize objects with immobile static charges.

#### Receipt and storage

MOS devices are packed for dispatch in antistatic/conductive containers, usually boxes, tubes or blister tape. The fact that the contents are sensitive to electrostatic discharge is shown by warning labels on both primary and secondary packing.

The devices should be kept in their original packing whilst in storage. If a bulk container is partially unpacked, the unpacking should be performed at a protected work station. Any MOS devices that are

stored temporarily should be packed in conductive or antistatic packing or carriers.

#### **Assembly**

MOS devices must be removed from their protective packing with earthed component pincers or short-circuit clips. Short-circuit clips must remain in place during mounting, soldering and cleansing/drying processes. Do not remove more devices from the storage packing than are needed at any one time. Production/assembly documents should state that the product contains electrostatic sensitive devices and that special precautions need to be taken. During assembly, ensure that the MOS devices are the last of the components to be mounted and that this is done at a protected work station.

All tools used during assembly, including soldering tools and solder baths, must be earthed. All hand tools should be of conductive or antistatic material and, where possible, should not be insulated.

Measuring and testing of completed circuit boards must be done at a protected work station. Place the soldered side of the circuit board on conductive or antistatic foam and remove the short-circuit clips. Remove the circuit board from the foam, holding the board only at the edges. Make sure the circuit board does not touch the conductive surface of the work bench. After testing, replace the circuit board on the conductive foam to await packing.

Assembled circuit boards containing MOS devices should be handled in the same way as unmounted MOS devices. They should also carry warning labels and be packed in conductive or antistatic packing.

# **Definition of data sheet status**

## **DEFINITIONS**

| Data sheet status                                                                                                  |                                                 |                                           |                                      |                                                     |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------|--------------------------------------|-----------------------------------------------------|

| Objective specification                                                                                            | This data sheet contai                          | ins target or goal sp                     | ecifications for prod                | luct development                                    |

| Preliminary specification                                                                                          | This data sheet contai                          | ins preliminary data;                     | supplementary dat                    | a may be published late                             |

| Product specification                                                                                              | This data sheet contai                          | ins final product spe                     | cifications                          |                                                     |

| Limiting values                                                                                                    |                                                 |                                           |                                      |                                                     |

| Limiting values given are<br>one or more of the limitir<br>and operating of the dev<br>of this specification is no | ng values may cause poice at these or any other | ermanent damage to<br>er conditions above | the device. These those given in the | are stress ratings only<br>Characteristics sections |

| Application information                                                                                            | )                                               |                                           |                                      |                                                     |

| Where application inform                                                                                           | ation is given, it is adv                       | isory and does not f                      | orm part of the spe                  | cification.                                         |

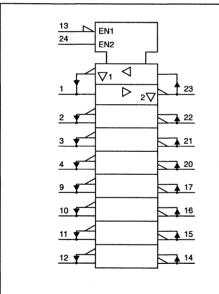

# Survey of pinouts

**HLL** series

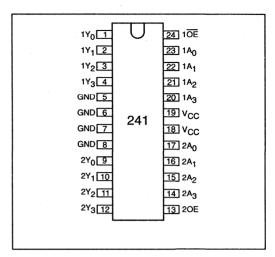

| 1Y <sub>0</sub> 1<br>1Y <sub>1</sub> 2<br>1Y <sub>2</sub> 3<br>1Y <sub>3</sub> 4<br>GND 5<br>GND 6<br>GND 7<br>GND 8<br>2Y <sub>0</sub> 9<br>2Y <sub>1</sub> 10<br>2Y <sub>2</sub> 11<br>2Y <sub>3</sub> 12 | 24 10E 23 1A <sub>0</sub> 22 1A <sub>1</sub> 21 1A <sub>2</sub> 20 1A <sub>3</sub> 19 V <sub>CC</sub> 18 V <sub>CC</sub> 17 2A <sub>0</sub> 16 2A <sub>1</sub> 15 2A <sub>2</sub> 14 2A <sub>3</sub> 13 20E |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

74HL33240

74HL33241

74HL33244

**HLL** series

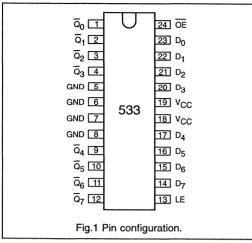

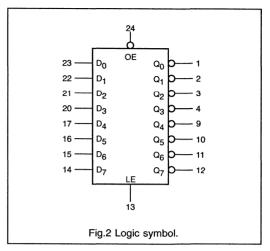

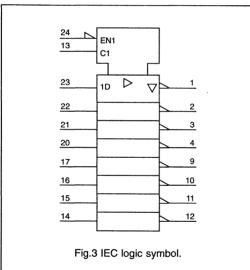

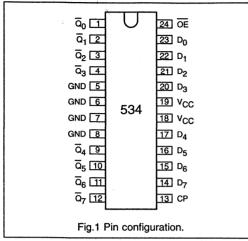

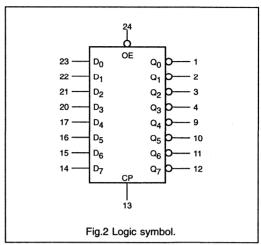

74HL33373

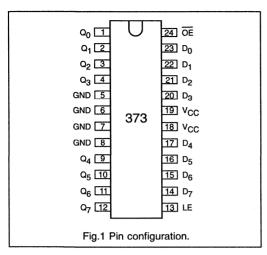

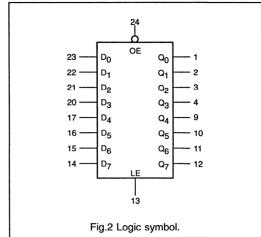

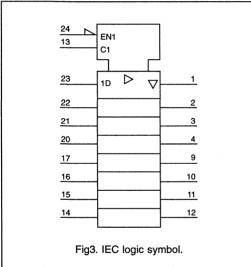

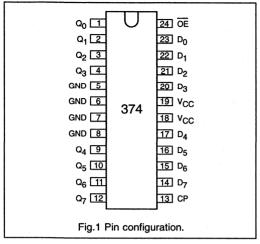

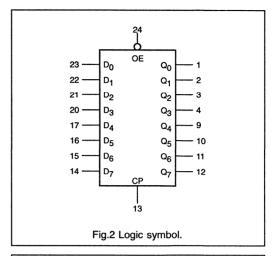

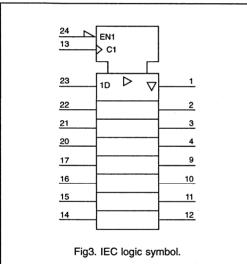

$\overline{Q}_0 \square$ 24 OE  $\overline{Q}_1$   $\boxed{2}$ 23 D<sub>0</sub>  $\overline{Q}_2$   $\boxed{3}$ 22 D<sub>1</sub>  $\overline{Q}_3$   $\boxed{4}$ 21 D<sub>2</sub> GND 5 20 D<sub>3</sub> 191 V<sub>CC</sub> GND 6 533 GND 7 18 V<sub>CC</sub> GND 8 17 D<sub>4</sub>  $\overline{Q}_4$   $\boxed{9}$ 16 D<sub>5</sub> Q<sub>5</sub> 10 15 D<sub>6</sub> ā<sub>6</sub> Ⅲ 14 D<sub>7</sub> Q<sub>7</sub> [12 13 LE

74HL33374

74HL33533

74HL33620

74HL33640

74HL33646

74HL33648

74HL33651

74HL33652

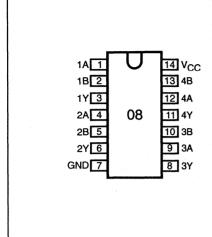

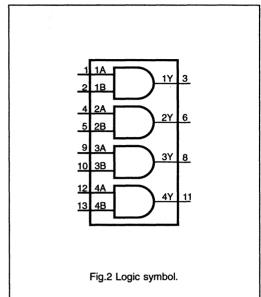

# Survey of pinouts

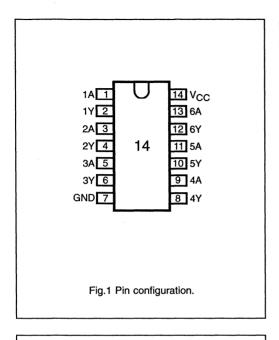

LV series

74LV00

74LV02

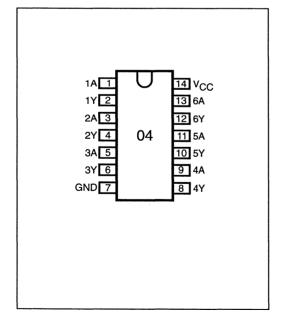

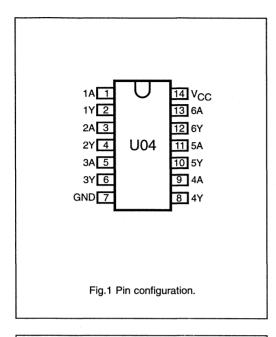

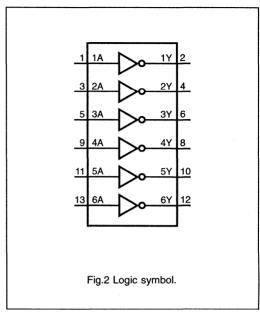

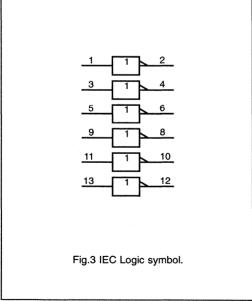

74LV04

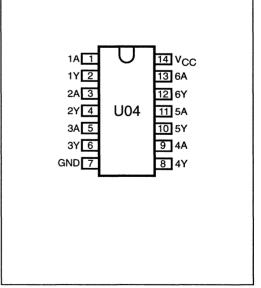

74LVU04

LV series

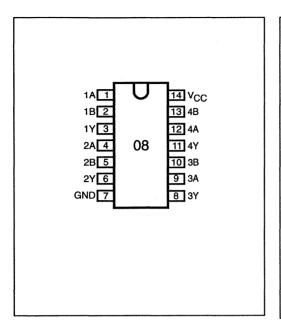

74LV08

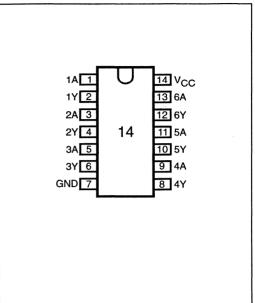

74LV14

74LV32

74LV74

LV series

74LV125

74LV138

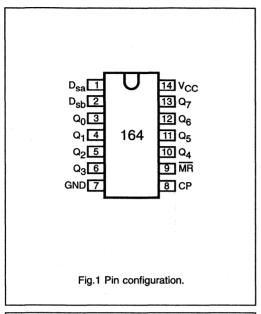

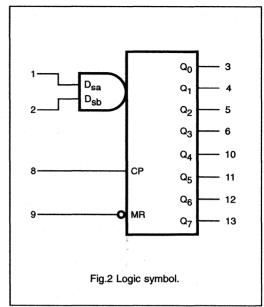

74LV139 74LV164

74LV174

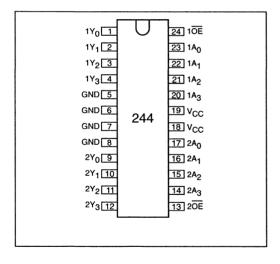

74LV244

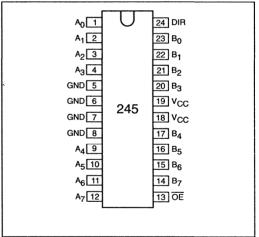

74LV245

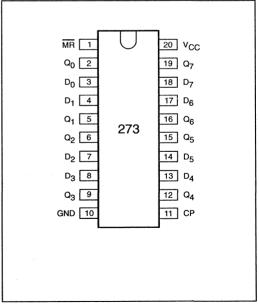

74LV273

# Survey of pinouts

LV series

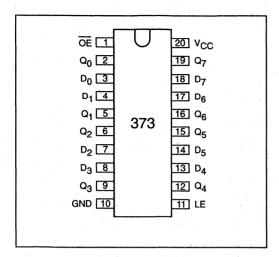

74LV373

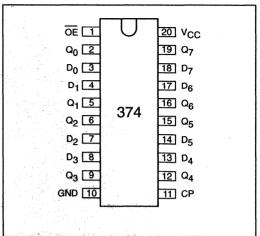

74LV374

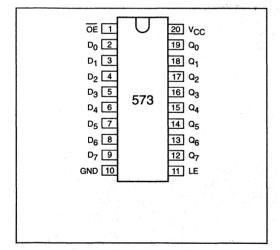

74LV573

74LV4066 74LV4094

DEVICE DATA

HLL family

# Octal buffer/line driver; 3-state; inverting

74HL33240

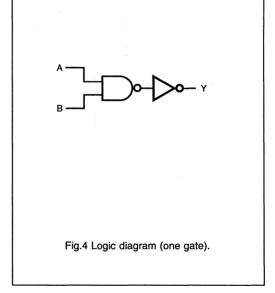

#### **FEATURES**